# Improvement of Luminance and Luminous Efficiency Using Address Voltage Pulse During Sustain-Period of AC-PDP

Sang-Hun Jang, Ki-Duck Cho, Heung-Sik Tae, Member, IEEE, Kyung Cheol Choi, and Seok-Hyun Lee

Abstract—To improve the luminance and luminous efficiency of a surface-discharge alternate current plasma display panel (ac PDP), auxiliary voltage pulses were applied to the address electrode during a sustain-period. The luminance and luminous efficiency exhibited maximum values at an address voltage of 100 V and pulse width of 1  $\mu$ s. An improved luminance of 21.4% and luminous efficiency of 24% were simultaneously obtained based on the proper adjustment of the widths and amplitudes of the address voltage pulses. Accordingly, the proper control of the amplitudes and pulse widths of the auxiliary address voltage during a sustain-period can improve both the luminance and the luminous efficiency in a surface-discharge ac PDP.

Index Terms—AC-PDPs, address voltage pulse, luminance, luminous efficiency.

### I. INTRODUCTION

PLASMA display panel (PDP) is one of the most promising flat panel devices for large area (>40 in) full color wall hanging digital high definition televisions (HDTVs) [1]. However, for the successful realization of commercial full color HDTVs, further improvements are needed in the PDP device, especially in the luminance and luminous efficiency [2]-[4]. In general, as the sustain voltage increases to improve the luminance of an ac PDP, the discharge current also increases and the luminance tends to become saturated [5], thereby resulting in a reduced luminous efficiency. Recently, there has been a variety of research related to developing sustain pulse waveforms for improving luminous efficiency [6]–[8], however, the luminous efficiency has only been improved in a high frequency region of about 180 kHz, plus the luminance are somewhat reduced. Accordingly, new driving methods including driving waveforms need to be developed to improve both the luminance and the luminous efficiency of an ac PDP. Since the red, green, and blue visible lights for displaying information are emitted during a sustain-period, the development of a proper driving method for these sustain-periods could contribute to improving the luminance and luminous efficiency.

Manuscript received December 6, 2000; revised March 19, 2001. This work was supported by the Brain Korea 21 Project in 2001. The review of this paper was arranged by Editor J. Hynecek.

Publisher Item Identifier S 0018-9383(01)06918-0.

Therefore, an investigation of the effects of various sustain waveforms during a sustain-period is important in relation to improving the luminance and luminous efficiency in an ac PDP. In addition, the effects of the supply of address pulses to the address electrode during a sustain-period needs to be investigated to improve the luminance and luminous efficiency of an ac PDP. It has been reported that the ratio of the maximum luminance and the minimum luminance for displaying black as well as the display quality of shades of gray has been improved by applying a half of sustaining voltage to the address electrode during a sustain-period, resulting in improving the display quality of the PDP [9]. In that research, no negative high voltage was required, so that a simple, compact, inexpensive power source was employable for the PDP drive circuit [9]. Until now, however, research on driving methods for the improvement of luminance and luminous efficiency using the address electrode during a sustain-period has been neglected. The current authors believe that the proper application of the auxiliary address voltage to the address electrode during a sustain-period can cause the atoms near the address electrode to become excited due to the drift motion of the charge particles toward the address electrode, provided that the proper address voltages are applied only during a plasma discharge. This additional excitement of the atoms near the address electrode, including the main sustain discharge produced by the sustain voltage applied to the sustain electrode, can then improve the luminance and luminous efficiency of an ac PDP.

Accordingly, in this study auxiliary voltage pulses were applied to the address electrode during a sustain-period in order to improve both the luminance and the luminous efficiency of a surface-type ac PDP. The effects of the amplitudes and widths of the auxiliary address pulses on the improvement of the luminance and luminous efficiency were also examined.

## II. EXPERIMENT

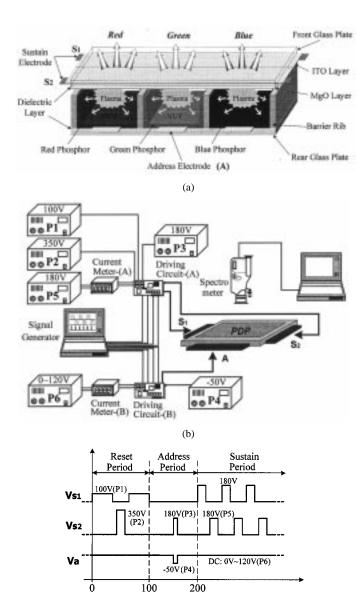

Fig. 1(a) shows the single pixel structure of the 4-in ac PDP test panel employed in this research. A single pixel is the minimum unit for displaying a full-color image, and consists of three cells that emit red, green, and blue lights based on the stimulation of R, G, and B phosphor layers by vacuum ultraviolet (VUV: 147 nm) produced from a He–Ne–Xe plasma discharge, respectively. The gray scale for the information display is then realized through the color combination of the red, green, and blue visible lights that are emitted as a result of the VUV stimulation of the R, G, and B phosphor layers in the three cells, re-

S. H. Jang, K. D. Cho, and H. S. Tae are with School of Electronic and Electrical Engineering, Kyungpook National University, Taegu 702-701, Korea (e-mail: hstae@ee.knu.ac.kr).

K. C. Choi is with Department of Electronic Engineering, Sejong University, Seoul 143-747, Korea.

S.-H. Lee is with School of Electrical Engineering, Inha University, Incheon 402-751. Korea

Fig. 1. Schematic diagram of an optical and electrical measurement system and its driving waveforms: (a) single pixel structure, (b) optical and electrical measurement system, and (c) voltage waveforms applied to three electrodes.

Time [msec]

(c)

spectively. The cell pitch of a single pixel was fixed at  $1080~\mu\mathrm{m}$ . On the front glass plate, the sustain electrodes  $(S_1, S_2)$  were covered with a dielectric layer 30  $\mu\mathrm{m}$  in thickness. An MgO protective layer with a thickness of 0.5  $\mu\mathrm{m}$  was then deposited on the dielectric layer. The widths of the sustain electrodes were  $260~\mu\mathrm{m}$ , respectively, and the gap between the sustain electrodes was  $100~\mu\mathrm{m}$ . The R,G, and B phosphors were deposited between the barrier ribs in the rear glass plate. The width of the address electrode (A) was  $100~\mu\mathrm{m}$  and the height of the barrier rib was  $120~\mu\mathrm{m}$ .

Fig. 1(b) shows a schematic diagram of the optical and electrical measurement system that was used to determine the luminance and luminous efficiency from the 4-in ac PDP test cell utilized in this study. The measurement system consists of a 4-in ac PDP test panel, its driving circuit system, a current meter, and a spectrometer. The driving circuit system consists of a pair

of driving circuits (A) and (B) and six power supplies  $P_1$ – $P_6$ . The driving circuit (A) was used to supply the electrical pulses to the sustain electrodes  $S_1$  and  $S_2$ , whereas the driving circuit (B) was used to supply the electrical pulses to the address electrode A. The  $P_1$  and  $P_2$  are the power supplies for applying the voltage pulses with 100 V and 350 V to the sustain electrodes  $S_1$  and  $S_2$  in a reset-period, respectively. The  $P_3$  and  $P_4$ are the power supplies for applying the voltage pulses with 180 V and -50 V to the sustain electrode  $S_2$  and the address electrode A in an address-period, respectively. The  $P_5$  and  $P_6$  are the power supplies for applying the voltage pulses with 180 V and 0 V-120 V to the sustain electrodes  $S_1$  and  $S_2$  and the address electrode A, respectively. The reset circuit (driving circuit (A), power supplies  $P_1$  and  $P_2$ ), the sustain circuit (driving circuit (A), power supply  $P_5$ ), and the address circuit (driving circuit (B), power supplies  $P_4$  and  $P_6$ ) were individually manufactured in order to investigate the effects of auxiliary address voltage pulses, which were applied to the address electrode during a sustain-period, on improving the luminance and luminous efficiency. The real current, which flowed through the three electrodes during a sustaining discharge, was measured as follows. The sustain current flowing through the sustain electrodes  $S_1$ and  $S_2$  during a sustain-period was measured in the power line between the driving circuit (A) and the power supply  $P_5$  by digital current meter (A), as shown in Fig. 1(b). The address current flowing through the address electrode A was also measured in another power line between the driving circuit (B) and the power supply  $P_6$  by digital current meters as shown in Fig. 1(b). The additional switch loss during a sustain-period was included in power consumption because the currents were measured in front of the driving circuits (A) and (B), as shown in Fig. 1(b). The luminance of the visible lights emitted from the 4-in ac PDP test panel was measured using a PR-704 spectrometer.

Fig. 1(c) shows the voltage waveforms applied to the three electrodes to drive the PDP test panel as illustrated in Fig. 1(b).  $V_{s1}$  and  $V_{s2}$  in Fig. 1(c) are the sustain voltage pulses applied to the sustain electrodes  $\mathcal{S}_1$  and  $\mathcal{S}_2$  shown on the front glass plate in Fig. 1(a), and the  $V_a$  in Fig. 1(c) is the address voltage pulse applied to the address electrode A shown on the rear glass plate in Fig. 1(a). The  $P_1$ – $P_6$  shown in Fig. 1(c) are the power supplies, as illustrated in Fig. 1(b). As shown in Fig. 1(c), the driving regions are divided into three periods, that is, reset, address, and sustain periods. During a reset-period, the wall charges generated in the previous sustain-period are erased, so that all the cells in the PDP have the same initial conditions. During an address-period, wall charges are accumulated from the space charge of the plasma discharge produced by the address voltage pulse in the address-period. Thereafter, only those cells with wall charges accumulated in the address-period can display information using the voltage waveform in the sustain-period. During a sustain-period, alternate voltage pulses are applied to the sustain electrodes  $S_1$  and  $S_2$  of all the cells, and a plasma discharge is then only produced in those cells with wall charges. At this point, no address voltage pulse is generally applied to the address electrode during the sustain-period, as shown in Fig. 1(c). In this work, the various address voltage pulses plus the sustain voltage pulse during a sustain-period are used to improve both the luminance and luminous efficiency.

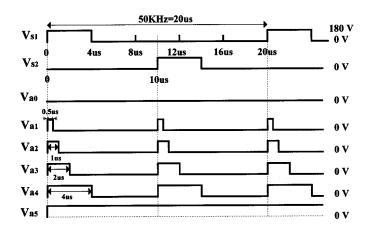

Fig. 2. Voltage pulse waveforms applied to three electrodes during sustain-period.

# III. RESULTS AND DISCUSSION

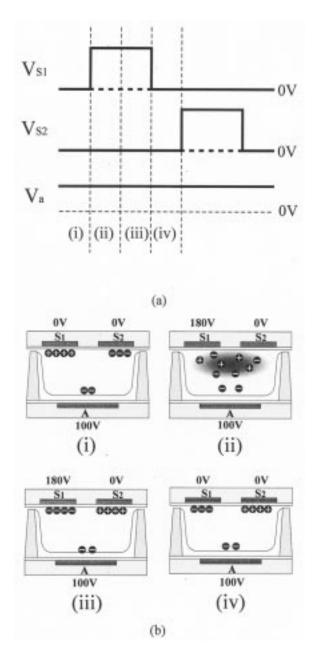

Fig. 2 shows the sustain driving voltage pulses  $V_{s1}$  and  $V_{s2}$ , and the corresponding address voltage pulses  $V_{a}$ .  $V_{s1}$  and  $V_{s2}$  are the sustain voltage pulses applied to the sustain electrodes during a sustain-period, respectively.  $V_{a0}, V_{a1}, V_{a2}, V_{a3}, V_{a4}$ , and  $V_{a5}$  are the address voltage pulses applied to the address electrode during a sustain-period, respectively, where  $V_{a0}$  indicates a zero voltage. The sustain voltage pulses and address voltage pulses were simultaneously applied to the three electrodes of the 4-in ac PDP test panel during a sustain-period, respectively. The amplitudes and pulse widths of the voltage pulses applied to the address electrodes vary from 20 V to 120 V, and from 0.5  $\mu$ s to infinity time (dc case), respectively. The other driving conditions are a sustain driving frequency of 50 kHz, a sustain voltage pulse width of 4  $\mu$ s, and a sustain voltage of 180 V.

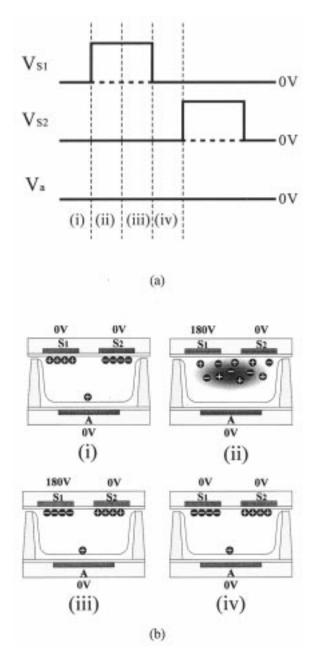

Fig. 3(a) shows the sustain voltage pulse waveforms,  $V_{s1}$  and  $V_{s2}$ , applied to the sustain electrodes during a sustain-period in the case of no auxiliary address voltage pulse  $V_a$ . The amplitudes of  $V_{s1}$  and  $V_{s2}$  were 180 V, respectively. Fig. 3(b) shows the corresponding temporal behavior model of the wall and space charges within the PDP cell with a variation in the only sustain voltage pulse waveform of Fig. 3(a) during the sustain-period [10], [11]. The driving scheme in Fig. 3(a) and the corresponding temporal behavior model in Fig. 3(b) represent the only sustain-period excluding the reset and address-period.

As shown in (i) of Fig. 3(a) and (b), wall charges, which had been produced by the previous sustain voltage pulse, were accumulated on the dielectric layer below the two sustain electrodes, while a very small amount of wall charges with a positive polarity were also accumulated on the phosphor layer above the address electrode. As the sustain voltage pulse  $V_{s1}$  applied to the sustain electrode  $S_1$  began to increase, as shown in (ii) of Fig. 3(a), and the electric field intensity generated by the sustain voltage of 180 V plus the accumulating wall charges satisfied the discharge condition, plasma was produced within the cell, as shown in (ii) of Fig. 3(b). At this point, since the electric field strength generated between the two sustain electrodes  $S_1$  and  $S_2$  was more stronger than that generated between the sustain electrode  $S_1$  and the address electrode  $S_2$  due to the short distance

Fig. 3. (a) Sustain voltage pulse waveforms without auxiliary address voltage pulse during sustain-period and (b) corresponding temporal behavior of wall/space charges within PDP cell.

between two sustain electrodes, the plasma within the cell was dominantly produced near the sustain electrode. The negatively charged particles, i.e., electrons of the space charges produced during this plasma discharge were accumulated on the sustain electrode  $S_1$  of 180 V with an opposite polarity to the electrons, whereas the positively charged particles, i.e., ions were accumulated on the sustain electrode  $S_2$  with 0 V, as shown in (iii) of Fig. 3(b). A negligible amount of ions were also accumulated on the address electrode with 0 V. As a result, in this case, the flow of the discharge current was only through the sustain electrode, and not through the address electrode. (Hereinafter, this current will be referred to as the 'main sustain discharge current') Thereafter, as shown in (iii) of Fig. 3(b), the plasma produced within the cell abruptly turned off because the accumula-

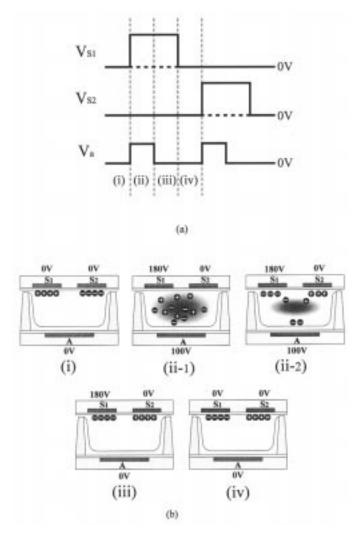

Fig. 4. (a) Sustain voltage pulse waveforms with time-varying auxiliary address voltage pulse during sustain-period and (b) corresponding temporal behavior of wall/space charges within PDP cell.

tion of the wall charges resulting from the space charges during a plasma discharge caused a reduction in the electric field intensity. Meanwhile, the sustain voltage of 180 V remained constant after the complete extinction of the plasma within the cell, thereby implying a continued application of the electric field generated by the sustain voltage of 180 V between the two sustain electrodes. Consequently, this electric field intensity will have a strong influence on the accumulation of wall charges, on which the next sustain discharge is comparatively dependent. The wall charges accumulated on the dielectric layer below the sustain electrodes remained constant until another sustain voltage pulse  $V_{s2}$  was applied to the sustain electrode, as shown in (iv) of Fig. 3(a) and (b).

Fig. 4(a) shows the sustain voltage pulse waveforms  $V_{s1}$  and  $V_{s2}$  in the case of applying the time-varying auxiliary address voltage pulse  $V_a$  to the address electrode. The amplitudes of  $V_{s1}$  and  $V_{s2}$  were 180 V, respectively, whereas the amplitude of  $V_a$  was 100 V. Fig. 4(b) shows the corresponding temporal behavior model of the wall and space charges within the PDP cell relative to the varied sustain voltage pulse and auxiliary address voltage pulse shown in Fig. 4(a) during a sustain-period. The driving

scheme in Fig. 4(a) and the corresponding temporal behavior model in Fig. 4(b) also represent the only sustain-period excluding the reset and address-period. Unlike (i) of Fig. 3(b), before the sustain voltage pulse  $V_{s1}$  was applied to the sustain electrode, no wall charges had accumulated on the phosphor layer above the address electrode, although most of the wall charges had accumulated on the dielectric layer below the two sustain electrodes, due to the previous sustain discharge, as shown in (i) of Fig. 4(b). As shown in (ii) of Fig. 4(a), the sustain voltage pulse  $V_{s1}$  and time-varying auxiliary address voltage pulse  $V_a$ were simultaneously applied to the sustain electrode  $S_1$  and address electrode A, respectively. When the electric field intensity generated by the sustain voltage plus by the wall charge accumulated during the previous sustain discharge satisfied the discharge condition, plasma was produced within the cell, as shown in (ii)-1 of Fig. 4(b). As the address pulse  $V_a$  was additionally applied to the address electrode A as shown in Fig. 4(a), the electric field was also induced between the sustain electrode  $S_2$ and the address electrode A due to the auxiliary address voltage. At this time, the space charged particles produced near the sustain electrodes by the sustain voltage pulse, particularly the electrons, began to be accelerated toward the address electrode, as shown in (ii)-1 of Fig. 4(b). Accordingly, unlike (ii) of Fig. 3(b), the plasma was produced between the sustain electrode and the address electrode as well as between two sustain electrodes. This indicates that this additional electric field induced by the address voltage can cause a drift motion of the charged particles, particularly electrons toward the address electrode if the charged particles produced by the sustaining discharge exist near the sustain electrodes. As a result, in this case, significant amount of negative space charges such as electrons were accumulated on the dielectric layer below the sustain electrode  $S_1$  with 180 V, whereas a small amount of negative space charges such as electrons was accumulated on the phosphor layer above the address electrode A with 100 V, as shown in (ii)-2 of Fig. 4(b). The positive space charges such as ions were accumulated on the dielectric layer below the sustain electrode  $S_2$  with 0 V. The plasma discharge intensity became weak due to the accumulation of the wall charges, as shown in (ii)-2 of Fig. 4(b). Finally, as shown in (iii) of Fig. 4(b), the plasma produced within the cell turned off due to the wall charges accumulated from the space charges. At this time, as shown in (iii) of Fig. 4(a), the address voltage  $V_a$  decreased abruptly from 100 V to 0 V, whereas the sustain voltage  $V_{s1}$  remained a constant value of 180 V. Accordingly, the wall charges accumulated on the dielectric layer below the two sustain electrode  $S_1$  and  $S_2$  remained nearly constant due to the sustain voltage difference of 180 V between two sustain electrodes, as shown in (iii) of Fig. 4(b). On the other hand, as the wall charges accumulated on the phosphor layer above the address electrode A were negative electrons, they were removed due to the voltage difference between the sustain voltage of 180 V and the address voltage of 0 V, as shown in (iii) of Fig. 4(b). As a result, in this case, the flow of the discharge current was not only through the main sustain electrodes but also through the auxiliary address electrode. (Hereinafter, this current flowing through the address electrode will be referred to as the auxiliary address discharge current) The distribution of the wall charge shown in (iii) of Fig. 4(b) remained constant until another sus-

Fig. 5. (a) Sustain voltage pulse waveforms with DC auxiliary address voltage pulse during sustain-period and (b) corresponding temporal behavior of wall/space charges within PDP cell.

tain voltage pulse  $V_{s2}$  and address voltage pulse  $V_a$  were applied to the sustain and address electrodes, respectively, as shown in (iv) of Fig. 4(b).

Fig. 5(a) shows the sustain voltage pulse waveforms  $V_{s1}$  and  $V_{s2}$  in the case of applying the dc auxiliary address voltage  $V_a$  to the address electrode. The amplitudes of  $V_{s1}$  and  $V_{s2}$  were 180 V, respectively, whereas the amplitude of  $V_a$  was 100 V. Fig. 5(b) shows the corresponding temporal behavior model of the wall and space charges within the PDP cell relative to the varied sustain voltage pulse and the auxiliary DC address voltage shown in Fig. 5(a) during a sustain-period. The driving scheme in Fig. 5(b) also represent the only sustain-period excluding the reset and address-period. Unlike (i) of Figs. 3(b) and

4(b), before the sustain voltage  $V_{s1}$  was applied to the sustain electrode, a small amount of wall charges with a negative polarity had accumulated on the phosphor layer above the address electrode, whereas most of the wall charges had accumulated on the dielectric layer below the two sustain electrodes, due to the previous sustain discharge, as shown in (i) of Fig. 5(b). As shown in (ii) of Fig. 5(a), the sustain voltage pulse  $V_{s1}$  and dc auxiliary address voltage  $V_a$  were simultaneously applied to the sustain electrode  $S_1$  and address electrode A, respectively. When the electric field intensity generated by the sustain voltage plus by the wall charge accumulated during the previous sustain discharge satisfied the discharge condition, plasma was produced within the cell, as shown in (ii) of Fig. 5(b). As the dc address pulse  $V_a$  was additionally applied to the address electrode A as shown in Fig. 5(a), the electric field was also induced between the sustain electrode  $S_2$  and the address electrode Adue to the auxiliary address voltage. Therefore, like (ii)-2 of Fig. 4(b), a significant amount of negative space charges such as electrons were accumulated on the dielectric layer below the sustain electrode  $S_1$  with 180 V, whereas a small amount of negative space charges such as electrons were also accumulated on the phosphor layer above the address electrode A with 100 V, as shown in (iii) of Fig. 5(b). As shown in (iii) of Fig. 5(b), the plasma produced within the cell turned off due to the wall charges accumulated from the space charges. However, unlike (iii) of Fig. 4(b), the negative wall charges on the phosphor layer above the address electrode remained constant because the constant address voltage of 100 V was applied to the address electrode. In the case of applying the dc address voltage, as shown in (iv) of Fig. 5(a), the address voltage remained 100 V even though the sustain voltage  $V_{s1}$  decreased from 180 V to 0 V. As a result, the appliance of the address voltage of 100 V at the sustain voltage of 0 V may disturb the amount or distribution of the wall charges with a negative polarity, which had been accumulated on the dielectric layer below the sustain electrode  $S_1$ after the complete extinction of the plasma, as shown in (iv) of Fig. 5(b).

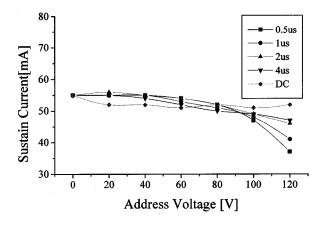

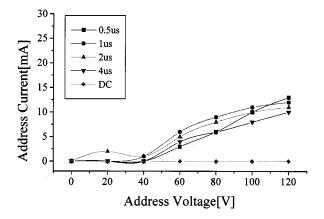

Fig. 6 shows the changes in the main sustain discharge current flowing through the sustain electrode during a sustain-period as a function of the address pulse voltage with various pulse widths. Fig. 7 shows the changes in the auxiliary address discharge current from the address electrode during a sustain-period as a function of the address pulse voltage with various pulse widths. When a sustain pulse was applied to the sustain electrode and an auxiliary address pulse was not applied to the address electrode, the main discharge current flowing through the sustain electrode was 55 mA, and there was no current flow through the address electrode. When the dc voltage was applied to the address electrode, the main discharge current in the sustain electrode decreased to a constant level of 52 mA and there was no auxiliary current flow through the address electrode. However, the reduced main sustain discharge current remained almost constant regardless of the increase in the dc address voltage.

This reduction of the main sustain discharge current indicates the weakness of the main sustain discharge itself. The dc voltage applied to the address electrode can produce the constant electric field, even though no current flows through the

Fig. 6. Changes in the main sustain discharge current from sustain electrode as a function of address voltage pulses with various widths and amplitudes.

Fig. 7. Changes in the auxiliary address discharge current from address electrode as a function of address voltage pulses with various pulse widths and amplitudes.

address electrode due to the dielectric layer including the phosphor layer on the address electrode. As mentioned in (iv) of Fig. 5(b), this constant electric field may affect the amount or distribution of the wall charges, which had been accumulated on the dielectric layer of the sustain electrode  $S_1$ . Accordingly, the reduction of the main sustain discharge current shown in Fig. 6 is thought to be presumably due to the disturbance of the wall charges necessary for the next sustain discharge. When a time-varying auxiliary address voltage was applied to the address electrode plus a sustain voltage pulse, the main sustain discharge current tended to decrease, whereas the auxiliary address discharge current tended to increase. However, in the case of a time-varying address voltage of less than 40 V, neither the main sustain discharge current nor the auxiliary address discharge current changed very much, as shown in Figs. 6 and 7.

With a time-varying address voltage greater than 40 V except the dc voltage, the main sustain discharge current began to decrease, whereas the auxiliary address discharge current began to increase. The supply of a time-varying auxiliary address voltage greater than 40 V means that a time-varying electric field affecting the drift motion of the space charges, such as electrons and ions, particularly electrons, is newly generated between the sustain electrode and the address electrode. Consequently, this electric field generated by the time-varying address voltage can

Fig. 8. Changes in luminance as a function of address voltage pulses with various pulse widths and amplitudes.

cause a drift motion of the electrons within the main sustain discharge plasma toward the address electrode. The resulting flow of space charges, such as electrons, toward the address electrode can then cause a simultaneous reduction in the main sustain discharge current in the sustain electrode and increase in the auxiliary address discharge current in the address electrode. As a result, the experimental result of Fig. 7 shows that the drift motion can be induced in our cell condition if the time-varying address voltage greater than 40 V is applied to the address electrode. However, in this case, all drift motions caused by the address voltage does not induce the additional excitement near the address electrode, which is a necessary condition for improving the luminance and luminous efficiency. In other words, there exist an optimal voltage for producing the additional excitement, and the proper value of the address voltage necessary for the additional excitement strongly depends on the discharge environments within a cell such as pressure, gas type, gas mixing ratio, shape of the phosphor layer, and so on. In addition, in order to improve the luminance and luminous efficiency by producing this additional excitement, careful attention must be taken not to perturb the accumulation of the wall charges on the dielectric layer below the sustain electrodes, which plays a significant role in the next sustain discharge.

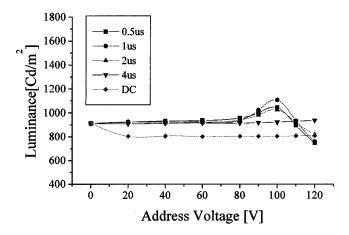

Fig. 8 shows the changes in luminance during a sustain-period as a function of the address pulse voltage with various pulse widths. As shown in Fig. 8, until the time-varying address voltage increased to the value of 80 V except dc case, the luminance was shown to be almost the same as that of an address voltage at 0 V, regardless of the pulse widths. However, as the time-varying address voltage with the pulse widths within a range of 0.5  $\mu$ s-2  $\mu$ s increased from 80 V to 120 V, the luminance was improved until the address voltage of 100 V, but reduced at the address voltage greater than 100 V. As shown in Fig. 8, in the case of pulse widths within a range of 0.5  $\mu$ s-2  $\mu$ s, the luminance was shown to be comparatively high at an address voltage of 100 V. Even though the time-varying address voltage below 80 V can induce a drift motion of electrons toward the address electrode, as shown in the data of address current in Fig. 7, this address voltage is too low to cause the atoms near the address electrode to be excited, thereby resulting in no affecting on

Fig. 9. Changes in the luminous efficiency as a function of address voltage pulses with various pulse widths and amplitudes.

the improvement of the luminance of the ac PDP. Furthermore, when the time-varying address voltage was greater than 100 V, particularly 120 V, the luminance fell abruptly to a low level, regardless of the pulse widths within a range of 0.5  $\mu$ s-2  $\mu$ s. This sudden reduction in the luminance of the ac PDP appeared to be due to a disturbance of the main sustain discharge between the sustain electrodes caused by an excessive address voltage (In this case, 120 V). In the case of dc address voltage, the luminance decreased to a constant level regardless of the amplitude of the address voltage. This reduction in the luminance at dc address voltage is thought to be presumably due to the disturbance of the wall charges caused by the remaining constant electric field after the complete extinction of the plasma discharge within a cell. These experimental results indicate that there is an optimal amplitude of the time-varying auxiliary address voltage for improving the luminance of the 4-in ac PDP test panel during a sustain-period. (In this case, 100 V) In the case of a pulse width wider than 2  $\mu$ s, the luminance did not improve, even at an address voltage of 100 V, as shown in Fig. 8, indicating that the luminance also depends on the pulse width of the address voltage as well as the amplitude of the address voltage. In this case, the pulse width wider than 2  $\mu$ s means that the auxiliary address voltage still remains after the complete extinction of the main sustain discharge. This time-varying auxiliary address voltage, which is still applied to the address electrode after the complete extinction of the main discharge, may disturb the distribution of the wall charges, which had already been accumulated during a main sustain discharge for the next sustain discharge. This result illustrates that the only auxiliary address voltage applied during a plasma discharge-on can be effective in improving the luminance of the 4-in ac PDP test panel. From the experimental result of Fig. 8, therefore, it is confirmed that there are an optimal amplitude and pulse width of the time-varying auxiliary address voltage for improving the luminance of the 4-in ac PDP test panel during a sustain-period.

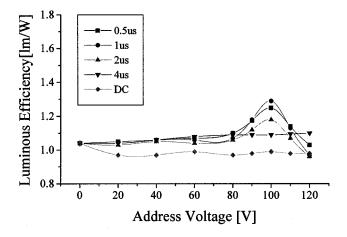

Fig. 9 shows the changes in the luminous efficiency during a sustain-period as a function of the address pulse voltage with various pulse widths. As shown in Fig. 9, the luminous efficiencies were also shown to be comparatively high in the case of pulse widths within a range of  $0.5 \,\mu\text{s} - 2 \,\mu\text{s}$ , at an address voltage

of 100 V. As such, the result in Fig. 9 is similar to that in Fig. 8. In conclusion, the proper control of the amplitude and pulse width of the auxiliary address voltage was required to improve the luminance and luminous efficiency of the ac PDP panel. As a result, an improved luminance of 21.4% and luminous efficiency of 24% were simultaneously obtained through the proper adjustment of the width and amplitude of the address voltage pulses.

# IV. CONCLUSION

The effects of auxiliary voltage pulses, which were applied to the address electrode during a sustain-period, on the improvement of luminance and luminous efficiency were investigated in the surface-discharge of a 4-in ac PDP test panel. The luminance and luminous efficiency were shown to be comparatively high in the case of pulse widths within a range of  $0.5~\mu s$ – $2~\mu s$ , at an address voltage of 100~V under sustain driving conditions including a voltage of 180~V and frequency of 50~kHz. Accordingly, based on the proper control of the address pulse width and its amplitude, an improved luminance of 21.4% and luminous efficiency of 24% were simultaneously achieved.

### REFERENCES

- [1] A. Sobel, "Plasma displays," *IEEE Trans. Plasma Sci.*, vol. 19, pp. 1032–1047, Dec. 1991.

- [2] T. Komaki, H. Taniguchi, and K. Amemiya, "High luminance AC-PDPs with Waffle-structured barrier ribs," in *Proc. IDW'99 Dig.*, 1999, pp. 587–590.

- [3] G. Oversluizen, S. de Zwart, S. van Heusden, and T. Dekker, "Improvement of luminance and luminous efficacy based on the investigation of Xe concentration and sustain voltage in PDPs," in *Proc. IDW'99 Dig.*, 1999, pp. 591–594.

- [4] K. J. Shin, J. H. Ryu, and M. H. Park, "A high luminous efficiency V-shaped electrode structure with a high Xe ratio gas," in *Proc. SID'99 Dig.*, 1999, pp. 544–547.

- [5] S. Mikoshiba, S. Shirai, S. Shinada, and M. Fukushima, "Saturation of Zn<sub>2</sub>SiO<sub>4</sub>:Mn luminescence under intense vuv excitation," *J. Appl. Phys.*, vol. 50, no. 2, pp. 1088–1090, Feb. 1979.

- [6] J. Kang, W. G. Jeon, and O. D. Kim et al., "Improvement of luminance and luminance efficiency in PDPs driven by radio frequency pulses," in Proc. IDW'99 Conf., 1999, pp. 691–694.

- [7] T. Hashimoto and A. Iwata, "Improvement of luminous efficiency in an AC PDP by self-erase discharge waveform," in *Proc. SID'99 Conf.*, 1999, pp. 540–543.

- [8] S.-T. Lo, C.-L. Chen, K.-M. Lee, and J.-F. Huang, "Improvement of luminous efficiency by a novel sustaining waveform for plasma display panels," in *Proc. SID'00 Dig.*, 2000, pp. 702–705.

- [9] Y. Kanazawa, "Method and apparatus for driving surface discharge plasma display panel," U.S. Patent 5 446 344, Aug. 29, 1995.

- [10] H. Hirakawa, T. Katayama, S. Kuroki, T. Kanae, H. Nanto, K. Yoshikawa, A. Otsuka, and M. Wakitani, "Cell structure and driving method of a 25-in. (64-cm) diagonal high-resolution color ac plasma display," in *Proc. SID'98 Dig.*, 1998, pp. 279–282.

- [11] C. Punset, S. Cany, and J.-P. Boeuf, "Addressing and sustaining in alternating current coplanar plasma display panels," *J. Appl. Phys.*, vol. 86, pp. 124–133, July 1999.

Sang-Hun Jang received the B.S. and M.S. degrees in electrical engineering from Kyungpook National University, Taegu, Korea, in 1996 and 1998, respectively, where he is currently pursuing the Ph.D. degree in electronic engineering.

His current research interests include the design and fabrication technique of new cell structure in an AC-PDP.

Mr. Jang is a student member of the Korean Information Display Society.

**Ki-Duck Cho** received the B.S. and M.S. degrees in electronic engineering from the Kyungpook National University, Taegu, Korea, in 1999 and 2001, respectively, where he is currently pursuing the Ph.D. degree in electronic engineering.

His current research interests include the driving circuit design of plasma display panels (PDPs).

Mr. Cho is a student member of the Korean Information Display Society.

**Kyung Cheol Choi** received the B.S. degree, the M.S. degree, and the Ph.D. degree in plasma engineering from Seoul National University, Seoul, Korea, in 1986, 1988, and 1993, respectively.

He was with the Institute for Advanced Engineering, Seoul, from 1993 to 1995, where his work focused on the design of field emission display devices. He was a Research Scientist in the Microbridge Plasma Display Panel, Spectron Corporation of America, Summit, NJ, from 1995 to 1996. He was a Senior Research Scientist at Hyundai Plasma

Display, Hawthorne, NY, from 1996 to 1998, where his work was to continue on developing plasma display technology. From 1998 to 1999, he was involved in the development of an ac 40 in Plasma Display Panel, Advanced Display R&D Center of Hyundai Electronics Industries, Kyoungki-do, South Korea as a Senior Research Scientist. Since March 1, 2000, he has been an Assistant Professor in the Department of Electronics, Sejong University, Seoul. His research interests include plasma display panel, field emission display, plasma engineering, and plasma modeling.

Dr. Choi is a member of the Korean Information Display Society.

**Heung-Sik Tae** (M'00) received the B.S. degree, M.S. degree, and Ph.D. degree in plasma engineering from Seoul National University, Seoul, Korea, in 1986, 1988, and 1994, respectively.

Since 1995, he has been as Associate Professor in the School of Electronic and Electrical Engineering, Kyungpook National University, Taegu, Korea. His research interests include the optical characterization and driving circuit of plasma display panel, the characterization for the luminous characteristics of phosphor layers in PDP using the plasma-stimulated

VUV source, the design of millimeter wave guiding structure, and MEMS or thick-film processing for millimeter wave device.

Dr. Tae is a member of the Korean Information Display Society.

Display Society.

**Seok-Hyun Lee** received the B.S. and M.S. degrees in electrical engineering and the Ph.D. degree in plasma engineering from Seoul National University, Seoul. Korea.

From 1993 to 1995, he was a Research Engineer at Hyundai Electronics. Since 1995, he has been an Associate Professor in electrical engineering at Inha University, Inchon, Korea. His research interests include plasma display, plasma simulation, and microwave-MEMS.

Dr. Lee is a member of the Korean Information